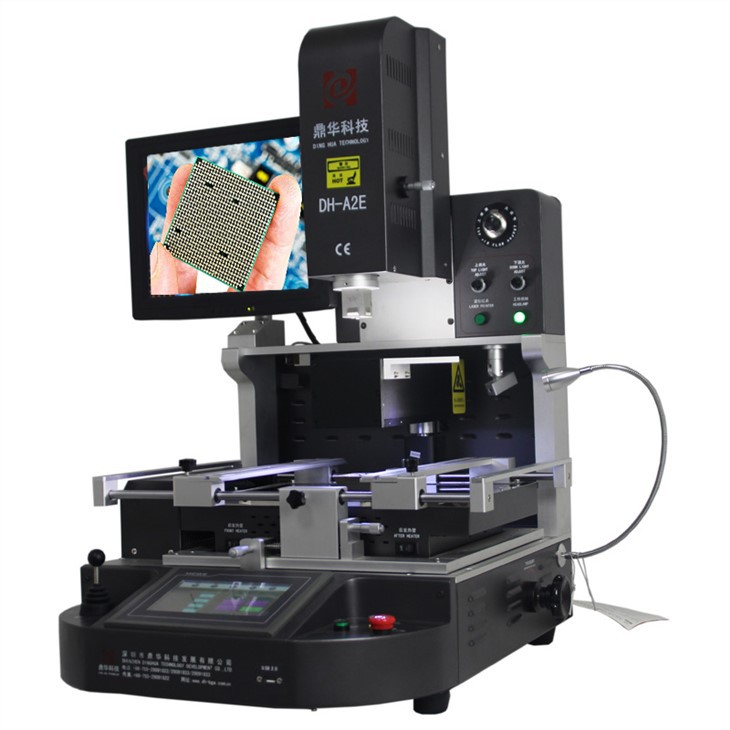

Auto optička BGA stanica za preradu

Široko se koristi u popravci na nivou čipa za matične ploče mobilnih, laptopa, računara, TV-a, klima uređaja itd. Ima visoku uspješnu stopu popravki i visok stepen automatizacije i štedi mnogo ljudskih napora. Mi smo profesionalni proizvođač ove mašine i imamo ove mašine na lageru.

Opis

Auto optička BGA stanica za preradu

1.Primjena Auto Optical BGA Rework Station

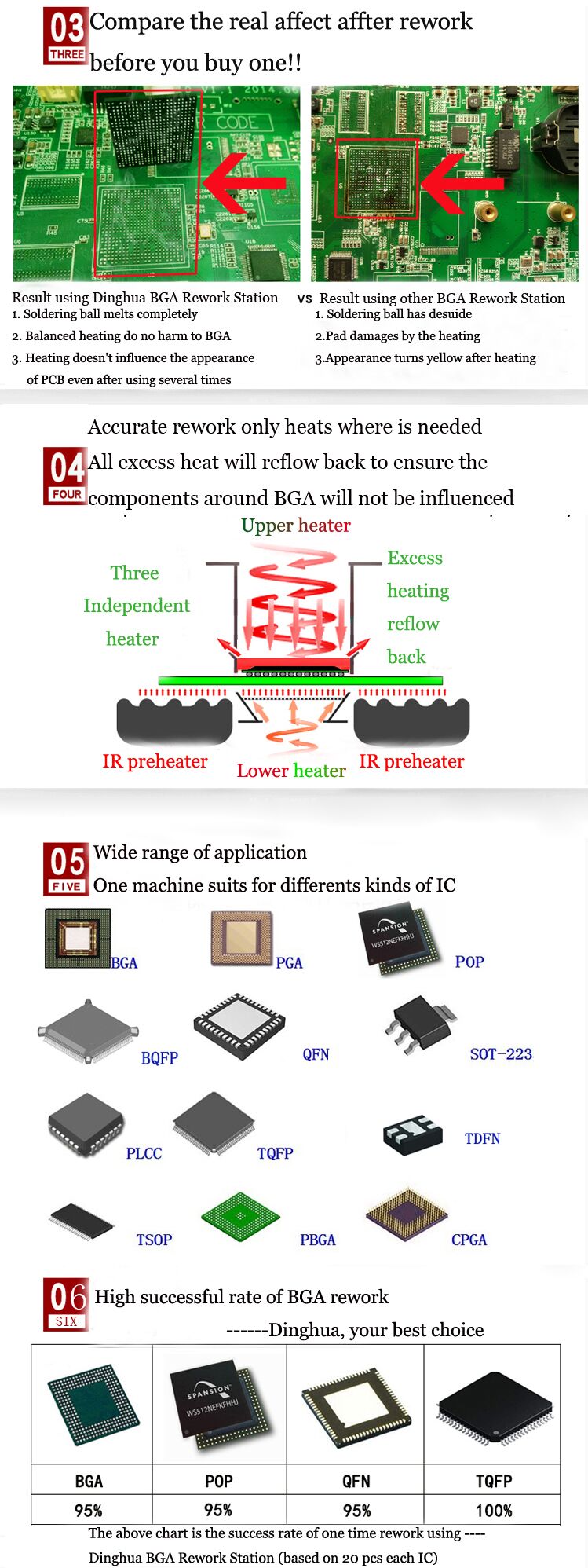

Matična ploča računara, pametnog telefona, laptopa, MacBook logičke ploče, digitalne kamere, klima uređaja, TV-a i druge elektronike

opreme iz medicinske industrije, industrije komunikacija, automobilske industrije itd.

Pogodno za različite vrste čipova: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED čip.

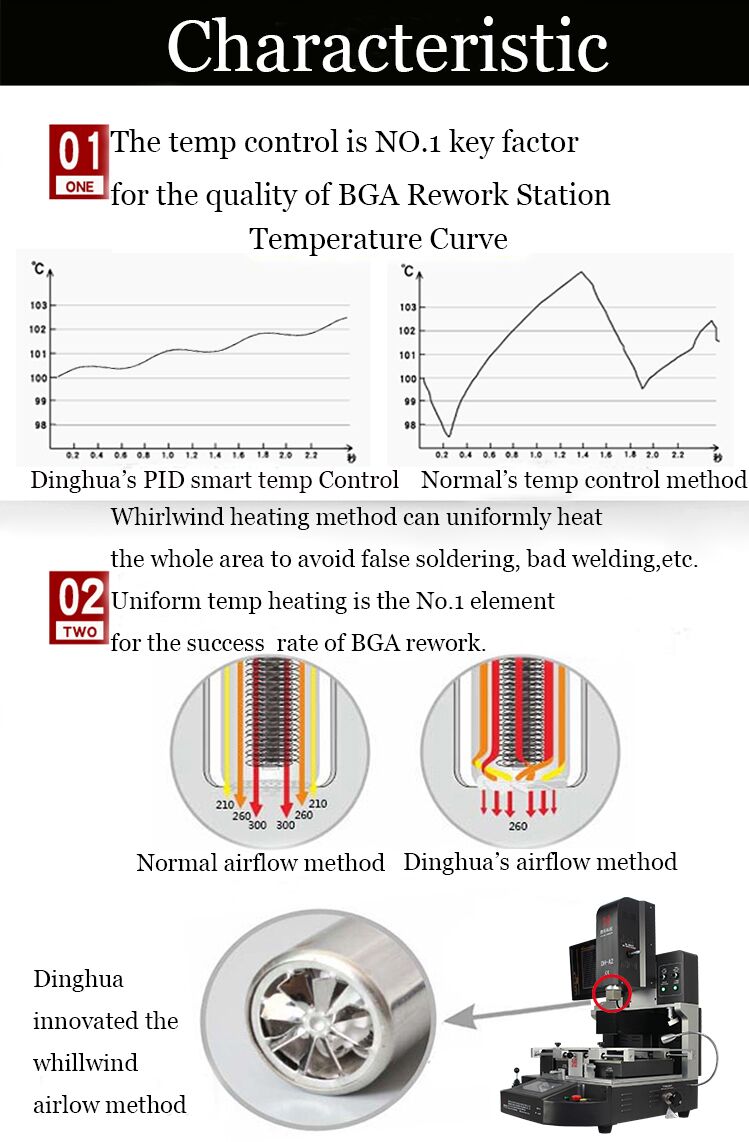

2. Karakteristike proizvoda Auto Optical BGA Rework Station

• Visoka uspješna stopa popravka na nivou strugotine. Proces odlemljenja, montaže i lemljenja je automatski.

• Precizno poravnanje svakog lemnog spoja može se garantovati sa CCD kamerom za optičko poravnanje.

•Precizna kontrola temperature može se osigurati sa 3 nezavisna područja grijanja. Mašina može podesiti i sačuvati

1 milion temperaturnog profila.

• Ugrađeni vakuum u montažnoj glavi automatski preuzima BGA čip nakon što je odlemljenje završeno.

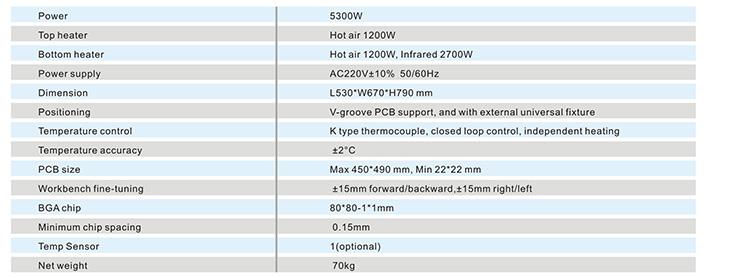

3.Specifikacija automatske optičke BGA stanice za preradu

4.Detalji automatske optičke BGA stanice za preradu

CCD kamera (precizan optički sistem poravnanja); 2.HD digitalni displej; 3. Mikrometar (podešavanje ugla čipa);

4.3 nezavisni grijači (topli zrak i infracrveni); 5. Lasersko pozicioniranje; 6. HD dodirni ekran interfejs, PLC kontrola;

7.Led far; 8. Kontrola džojstika .

5. Zašto odabrati našu Auto optičku BGA stanicu za preradu?

6. Certifikat Auto Optical BGA Rework Station

7. Pakovanje i isporuka Auto optičke BGA stanice za preradu

8.FAQ

Kako testirati čip?

Početni test čipa na nivou sistema

SoC je baziran na dubokim submikronskim procesima, tako da testiranje novih Soc uređaja zahtijeva potpuno novi pristup. Jer svaka funkcionalna komponenta

ima svoje zahtjeve za testiranje, projektant mora napraviti plan testiranja rano u procesu dizajna.

Plan testiranja blok po blok za SoC uređaje mora biti implementiran: pravilno konfigurisani ATPG alati za testiranje logike; kratko vrijeme testiranja; nove velike brzine

modeli grešaka i testovi višestruke memorije ili malih nizova. Za proizvodnu liniju, dijagnostička metoda ne samo da pronalazi grešku, već i razdvaja

neispravan čvor od radnog čvora. Osim toga, treba koristiti tehnike multipleksiranja testova kad god je to moguće kako bi se uštedjelo vrijeme testiranja. U oblasti visoko

integrisano IC testiranje, ATPG i IDDQ tehnike dizajna koje se mogu testirati imaju moćan mehanizam za razdvajanje grešaka.

Drugi stvarni parametri koje je potrebno unaprijed planirati uključuju broj pinova koje treba skenirati i količinu memorije na svakom kraju pinova.

Granična skeniranja mogu biti ugrađena u SoC, ali nisu ograničena na testove međusobnog povezivanja na pločama ili modulima s više čipova.

Iako se veličina čipa smanjuje, čip i dalje može upakovati milione do 100 miliona tranzistora, a broj testnih modova porastao je na neviđeno

nivoa, što rezultira dužim ciklusima testiranja. Ovaj problem se može testirati. Način kompresije za rješavanje, omjer kompresije može doseći 20 posto do 60 posto. Za današnje velike

dizajn čipa, kako bi se izbjegli problemi sa kapacitetom, potrebno je pronaći testni softver koji može raditi na 64-bitnim operativnim sistemima.

Osim toga, testni softver se suočava s novim problemima testiranja uzrokovanim dubokim submikronskim procesima i sve većom učestalošću. U prošlosti je ATPG test mod za

testiranje kvarova statičkog blokiranja više nije bilo primjenjivo. Dodavanje funkcionalnih obrazaca tradicionalnim alatima otežavalo je pronalaženje novih grešaka. Bolji pristup je da

klasificirati prošle funkcionalne grupe načina kako bi se utvrdilo koje greške ne mogu biti otkrivene, a zatim kreirajte ATPG način rada za hvatanje ovih nedostajućih tipova grešaka.

Kako se projektni kapacitet povećava i vrijeme testiranja po tranzistoru smanjuje, kako bi se pronašli problemi povezani s brzinom i provjerili vrijeme kola, sinhrona metoda ispitivanja

mora biti zaposlen. Sinhrono testiranje mora uključiti višestruke modele grešaka, uključujući modele prijelaza, kašnjenja putanje i IDDQ.

Neke kompanije u industriji vjeruju da kombinacija blokiranja, funkcionalnih i grešaka prolaznog/kašnjenja putanje može biti najefikasnija strategija testiranja. Za duboko

submikronski čipovi i visokofrekventni rad, testiranje tranzijenta i kašnjenja putanje je još važnije.

Da bi se riješio problem ATE tačnosti pri sinhronizaciji testnog jezgra i smanjio trošak, potrebno je pronaći novu metodu koja pojednostavljuje sučelje

testni uređaj (test prolaznog stanja i kašnjenja putanje zahtijeva tačan sat na interfejsu uređaja za testiranje), osigurava da je signal dovoljno tačan tokom testa.

Budući da postoji velika mogućnost proizvodnih grešaka u SoC memorijskom bloku, memorijski BIST mora imati dijagnostičku funkciju. Kada se problem pronađe,

defektna adresna jedinica se može mapirati u redundantnu memoriju rezervne adresne jedinice, a otkrivena adresa greške će biti odbačena. Izbjegavajte odbacivanje

ceo skupi čip.

Testiranje malih ugrađenih memorijskih blokova eliminira potrebu za dodatnim vratima ili kontrolnom logikom. Na primjer, tehnike testiranja vektorske konverzije mogu konvertirati

funkcionalne modove u niz modova skeniranja.

Za razliku od BIST metode, funkcionalni ulaz zaobilaznog memorijskog bloka ne zahtijeva dodatnu logiku. Budući da nije potrebna dodatna testna logika, SoC

razvojni inženjeri mogu ponovo koristiti testne obrasce koji su formirani u prošlosti.

Napredni ATPG alati ne samo da paralelno testiraju makroe, već i određuju da li postoje konflikti, kao i detaljan opis koji makroi se mogu testirati paralelno, a koji

makroi se ne mogu testirati paralelno. Osim toga, ovi makroi se mogu efikasno testirati čak i ako je sat makroa isti kao sat skeniranja (kao što je sinhrona memorija).

Trenutno nema dovoljno testnih tačaka na gustoj dvostranoj ploči, a svaki složeni čip mora biti opremljen graničnim krugom za skeniranje. Bez

skeniranje granica, traženje grešaka u proizvodnji na nivou ploče su prilično teške i ne mogu se čak ni pronaći. Sa skeniranjem granica, testiranje na nivou ploče je izuzetno jednostavno

i nezavisno od logičkih kola unutar čipa. Granično skeniranje također može konfigurirati ATPG način rada za lanac skeniranja čipa u bilo kojoj fazi proizvodnje.